Hackable Magazine 55

Circuits programmables / VHDL / Z80 :

Mon premier (vrai) projet FPGA !

- Choisir sa plateforme

- Réunir CPU, RAM, ROM et UART

- Créer son ordinateur 8 bits

14,90 € TTC

Anciens Numéros

Outils & Logiciels

p. 04 Alimentation de laboratoire ALIENTEK DP100 : petite, mais costaud

p. 18 Un oscilloscope à pédale

Sécurité

p. 34 Concevoir, mettre en place et bidouiller un environnement basé sur le protocole industriel Modbus

FPGA & Gateware

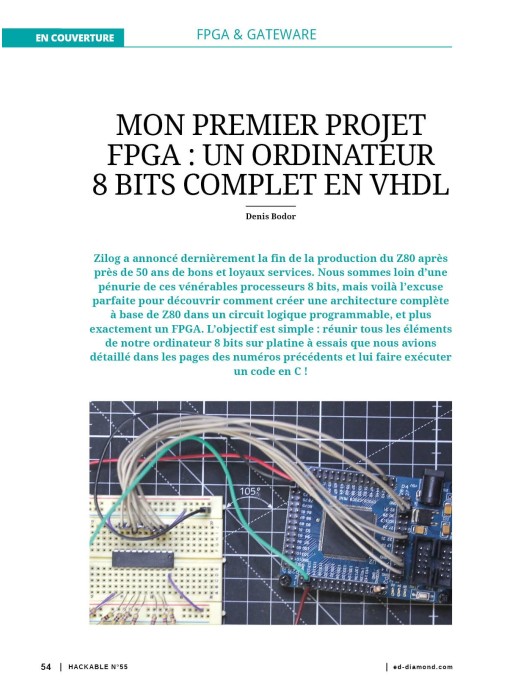

p. 54 Mon premier projet FPGA : un ordinateur 8 bits complet en VHDL

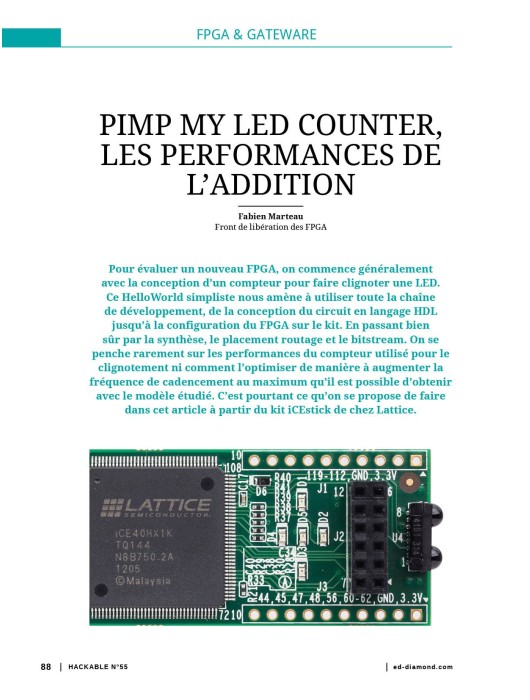

p. 88 Pimp my LED counter, les performances de l’addition

Rétro

p. 112 Asterisk, RTC, PPP, CPC 464... Surfons comme en 1989 !

Quelque chose est sur le point de changer dans l’embarqué... et pas seulement.

La sécurité des systèmes est plus que jamais sur le devant de la scène. L’industrie entière s’est enfin rendu compte des répercussions potentiellement catastrophiques de failles de sécurité au plus bas niveau et redouble d’efforts pour « régler » le problème. Mais on a beau tenter de « sécuriser » les systèmes, les applications, les services et même les langages, si une faiblesse existe, héritée de plusieurs dizaines d’années d’histoire de l’informatique moderne, elle sera forcément exploitée. Cette faiblesse est la manière dont l’accès à la mémoire est géré par les processeurs et la corruption de cette mémoire, d’une façon ou d’une autre, représente statistiquement la principale cause des failles de sécurité.

Pour régler le problème, un nouveau paradigme a vu le jour et est sur le point de se généraliser, en particulier dans l’embarqué (dans un premier temps) : les capabilities et plus exactement l’adressage mémoire basée sur les capabilities. Le concept n’est pas nouveau, puisqu’il s’agit simplement d’associer une métadonnée à un objet (au sens large du terme), pour conférer ou non une « capacité » (d’où le nom) à manipuler cet objet. Ce qui est (presque) nouveau, en revanche, c’est d’intégrer ce mécanisme dans le processeur lui-même sous la forme d’une gestion mémoire étendue et d’instructions spécifiques. « Presque », parce que le System/38 d’IBM (1978) utilisait cette technologie, mais depuis, le mécanisme de pagination mémoire a été universellement adopté.

Le projet vers lequel convergent les recherches depuis quelque temps est celui de l’université de Cambridge : CHERI (pour Capability Hardware Enhanced Risc Instructions). Les constructeurs (ARM en tête avec son projet Morello, mais RISC-V n’est pas en reste), les éditeurs de logiciels, ainsi que les projets open source (Morello Linux, CheriBSD, LLVM, FreeRTOS, etc.) forcent la marche pour nous rapprocher d’un premier produit fini.

Difficile de prédire quand cette révolution aura lieu, et débarquera dans nos smartphones et nos SBC, mais elle est en route, et ça changera énormément de choses...

Denis Bodor

Le bimestriel spécialisé dans l'électronique numérique et l'embarqué !

Né en 2014, Hackable est un bimestriel destiné aux professionnels et particuliers souhaitant découvrir et progresser dans les domaines de l’électronique numérique et de l’embarqué. Il fournit un contenu riche orienté vers une audience désireuse de bénéficier d'une veille technologique différente et résolument pratique. Le contenu du magazine est conçu de manière à permettre une mise en pratique directe des connaissances acquises et apprendre tout en faisant.

Perplexe, voilà l’état dans lequel j’ai été lorsque l’on m’a annoncé que j’allais m’occuper d’un hors-série consacré à la Raspberry Pi. Là où tout le monde me disait, « tu verras, c’est comme un ordinateur », je pensais « mais que vais-je faire avec cet espèce de circuit imprimé, cette carte si petite que je pourrais la glisser dans mon portefeuille ? ». Alors que je rédige cette préface au terme de la rédaction de ce numéro spécial, je sais désormais que les apparences sont trompeuses. Ce projet, outre son nom gourmand (je profite de ces lignes pour déclarer mon amour pour les framboises), a des pouvoirs insoupçonnés.